logiCORE PCI

Initiator Data Phase Control

この章では、ユーザーアプリケーションがデータのソースまたはシンクの能力に合わせてイニシエータートランザクションの側面を制御する方法について説明します。

ユーザーアプリケーションは、最初のデータ転送の前に待機状態を挿入して、準備ができていない場合には追加の時間を可能にします。

さらに、ユーザーアプリケーションは、トランザクションを完了する時期を示すことによってデータフェーズの数を制御できます。

可能な限り、待機状態での初期レイテンシの生成はお勧めできません。

この手法は、貴重なバス帯域幅を浪費します。

帯域幅の観点からは、トランザクションを実行する準備が整うまで、ユーザーアプリケーションがバス要求の作成を遅らせる方がよいでしょう。

Control Modes

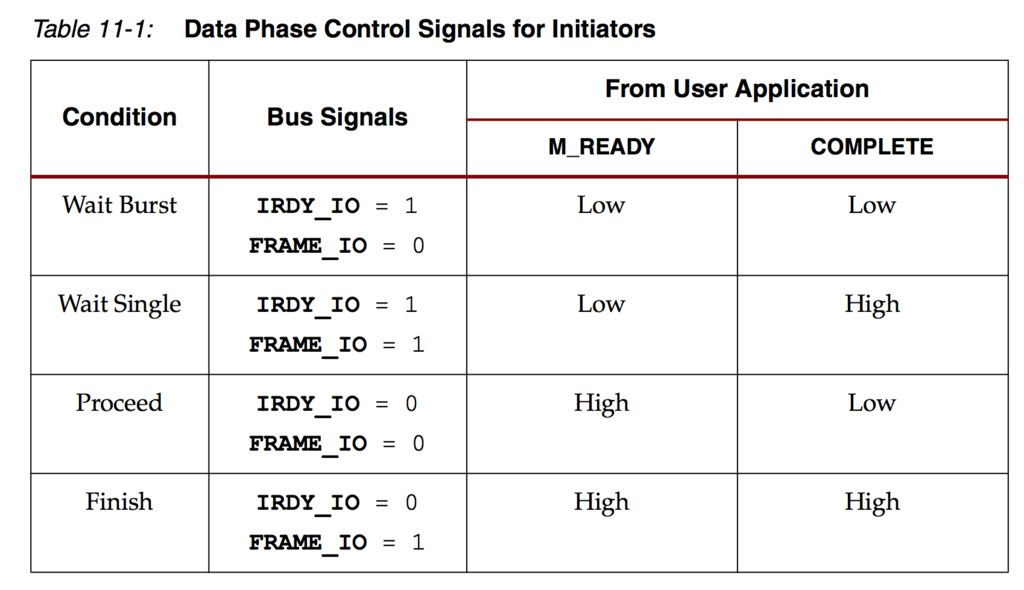

データ位相制御は、M_READYおよびCOMPLETE信号を使用して実現されます。

2つの制御信号の組み合わせは、以下のモードを含む。

Wait BurstはPCIインターフェイスによるIRDY_IOのアサートを遅延させることによって、 PCIバストランザクションの開始時にウェイトステートを挿入します(最初のデータフェーズを保持します)。

この特定の待機モードは、イニシエータバーストトランザクションで使用するためのものです。

このモードを使用すると、PCIインターフェイスに、ユーザーアプリケーションが準備ができていないことが示され、複数のデータフェーズが試行されます。Wait Singleはウェイトバーストモードと同じ方法で、PCIバストランザクションの開始時にウェイトを挿入します。

ただし、このモードは単一のイニシエータトランザクションで使用するためのモードです。

このモードの使用は、PCIインターフェイスに対して、ユーザアプリケーションが準備ができておらず、複数のデータフェーズを試みないことを示します。ProceedはPCIバスのデータフェーズを中断することなく進めることを可能にします。

選択したターゲットが待機状態を挿入したり、トランザクションを途中で終了したりすることがありますが、ユーザーアプリケーションはデータをフルスピードで転送する準備が必要です。

これは、複数のデータフェーズ転送でのみ使用できます。Finishを使用すると、PCIインターフェイスはできるだけ早くトランザクションを完了します。

これは、単一および複数のデータフェーズ転送の両方で使用するためのものです。

ここでも、正確な切断シーケンスは、選択されたターゲットがトランザクションを終了するかどうかによって影響されます。

PCIインターフェイスは自動的に正しい動作を生成します。

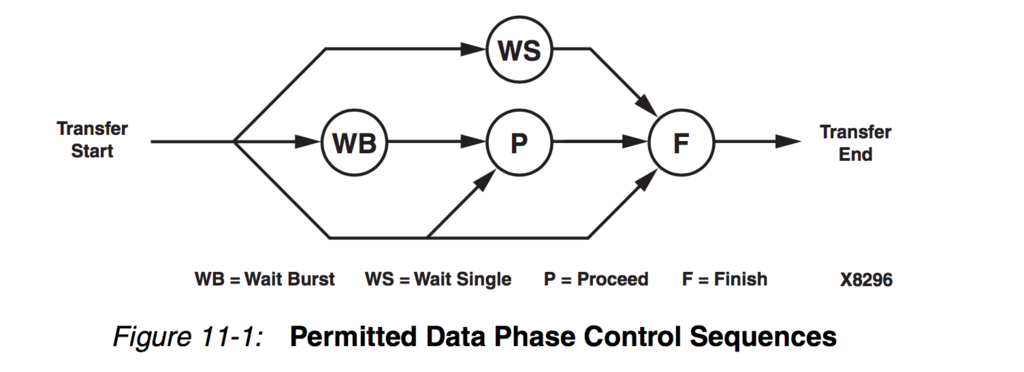

あるモードから別のモードへの変更は、任意の順序で行うべきではありません。

さらに、トランザクションで発生するデータフェーズの数を正確に制御するためには、モード遷移のタイミングが重要です。

これは、フィニッシュモードに切り替えるときに特に重要です。

図11-1に、PCIインタフェースを使用したイニシエータデザインの許可されたデータ位相制御シーケンスを示します。

正確なタイミングの詳細は、この章の次のセクションで定義されています。

図11-1に示す制御シーケンスは、ユーザーアプリケーションがトランザクションを終了していることを前提としています。

実際には、トランザクションは、ターゲットアプリケーションの終了やタイムアウトなど、ユーザーアプリケーションが制御できない理由で終了することがあります。

そのような状態の後にイニシエータ状態マシンが非アクティブになると、シーケンシングルールはもはや適用されない。

厳しいPCIバスのパフォーマンス要件を満たすために、PCIインターフェイスはすべてのバス制御信号とデータパスをパイプラインします。

したがって、M_READY信号およびCOMPLETE信号は、所望の効果の前に提示されなければならない。

ウェイトモードは、トランザクション内の任意のデータフェーズでウェイトステートを挿入するために使用できないことに注意してください。

これらは、イニシエータトランザクションの最初のデータフェーズの完了を遅延させるためにのみ使用できます。

これは、PCIローカルバス仕様ではマスタデータレイテンシと呼ばれます。

すべてのイニシエータは、FRAME_IOのアサートから8クロック以内にトランザクションの最初のデータフェーズを完了する必要があります。

PCIローカルバス仕様は、マスタデータレイテンシの使用を強く推奨しておらず、一般的にそれを使用する理由はないと述べています。

ユーザアプリケーションは、この要件を遵守する責任があります。

信号M_READYおよびCOMPLETEは、複数の論理レベルを介してイニシエータ状態マシンに接続する。

このため、これらの信号を駆動するロジックをできるだけシンプルに保つことを強く推奨します。

これらの信号をユーザアプリケーションのフリップフロップからドライブすることは有益ですが、これは典型的には最も単純な(バーストではない)デザイン以外では不可能です。

Control Pipeline

ユーザアプリケーションは、REQUESTをアサートしてから1サイクル以内に、正しい初期データ位相制御モードを提示しなければなりません。

この後、図11-1に示すシーケンシングに違反しない限り、ユーザーアプリケーションはモードを変更できます。

いずれの場合も、ユーザアプリケーションがイニシエータトランザクションの終了を決定すると、M_READYとCOMPLETEを適切に設定して終了モードを選択する必要があります。

ユーザアプリケーションがトランザクションを終了することを通知すると、トランザクションの終了時までM_READYおよびCOMPLETEを保持する必要があります。

PCIインタフェースによるM_DATAのアサーション解除は、転送が終了したことを示します。

Transaction Termination Rules

ユーザアプリケーションが単一のデータワードを送信または受信している場合、

ユーザアプリケーションは、REQUESTをアサートしてから1サイクル以内に待機シングルモードまたは終了モードを通知する必要があります。

ユーザアプリケーションがウェイトシングルモードを使用してウェイトステートを挿入する場合は、

PCIインタフェースがマスタデータレイテンシ仕様に違反する前に終了モードに切り替える必要があります。

再び、ユーザーアプリケーションがトランザクションを終了するように信号を送ると、

M_DATA状態の終わりまでM_READYとCOMPLETEを保持する必要があります。

ユーザアプリケーションが2つのデータワードを送信または受信している場合、ユーザアプリケーションは、ウェイトバーストまたは進行モードのいずれかで開始することができる。

ウェイトバーストモードで開始する場合、ユーザインターフェイスは、PCIインターフェイスがマスタデータレイテンシ仕様に違反する前に、進行モードに切り替える必要があります。

進行モードに入ると、次の両方の条件が満たされると、ユーザーアプリケーションは終了モードに切り替える必要があります。

- 進行モードは、少なくとも1サイクル

- 信号M_DATAが少なくとも1サイクルアサートされている

3つ以上のデータワードのバースト転送の場合、初期モード選択は2転送の場合と同じである。

3つの転送が残り、M_DATA_VLDがアサートされると、ユーザアプリケーションは終了モードに切り替える必要があります。

Implementation

上に示した規則はテキストで表示すると複雑に見えますが、次の例では一般的なケースでM_READYとCOMPLETEを駆動するために必要なロジックを示します。

この例は、前の章で示した例を基にしており、簡単なバースト転送を実行できます。

このコードは、M_READYとCOMPLETEを生成した以前のロジックを置き換えます。

ほとんどのイニシエータ設計では、転送カウンタを使用して希望のバースト長を追跡します。

次のロジックは転送カウンタを実装し、残りの転送数を示す3つの出力を生成します。

BURST_LENGTHおよびSTART信号は、ユーザアプリケーション内の他の場所で生成されます。

読み書きの場合、M_DATA_VLDは、PCIバス上のデータ転送が成功したことを示すために使用されます。

次のロジックは、後でM_READYおよびCOMPLETEロジックで使用されるイニシエータレディ信号を生成します。

イニシエータとしてウェイトステートを挿入しないユーザアプリケーション設計では、このロジックを最適化することができます。

ロジックは、READY_FLAGという信号をサンプリングします。この信号は、ユーザーアプリケーションの別の場所で生成されます。

この信号は、ユーザーアプリケーションがデータを転送する準備ができていることを示します。

最後のステップは、M_READYとCOMPLETEを生成することです。

典型的には、イニシエータ待ち状態は使用されず、INIT_WAITED信号は方程式から最適化されるべきである。

タイミングの理由から可能な限りロジックを減らすことが重要です。